据相关报道,英特尔已完成其英特尔 18A(1.8 纳米级)和英特尔 20A(2 纳米级)制造工艺的开发,这些工艺将用于制造公司自己的产品,以及为其英特尔代工服务 (IFS) 部门的客户生产的芯片。但这并不意味着生产节点已准备好用于商业制造,而是英特尔已经确定了这两种技术的所有规格、材料、要求和性能目标。

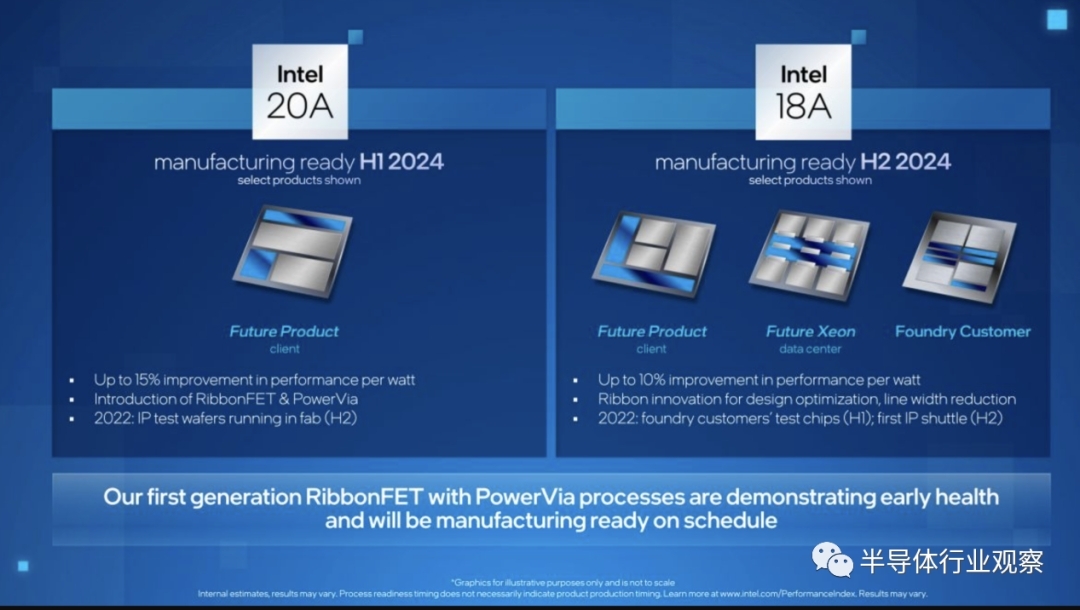

英特尔的 20A 制造技术将依赖环栅 RibbonFET 晶体管,并将使用背面供电。缩小金属间距、引入全新的晶体管结构并同时增加背面供电是一个冒险的举动,但预计 20A 将使英特尔超越公司的竞争对手——台积电和三星代工厂。英特尔计划在 2024 年上半年开始使用该节点。

英特尔的 18A 制造工艺将进一步完善公司的 RibbonFET 和 PowerVia 技术,并缩小晶体管尺寸。该节点的开发显然进展顺利,以至于英特尔将其推出时间从 2025 年推迟到 2024 年下半年。英特尔最初计划为其 1.8 埃节点使用具有 0.55 数值孔径 (NA) 光学器件的 ASML Twinscan EXE 扫描仪,但由于它决定尽快开始使用该技术,它将不得不依赖于大量使用具有 0.33 NA 光学器件的现有 Twinscan NXE 扫描仪,以及 EUV 双图案化。

该公司本身预计其 1.8 纳米级制造技术将在 2024 年下半年进入大批量制造 (HVM) 时成为业界最先进的节点。

英特尔的 20A 和 18A 制造技术正在为公司自己的产品以及 IFS 为其代工客户生产的芯片而开发。

英特尔首席执行官帕特·基辛格 (Pat Gelsinger) 在最近与分析师举行的电话会议上表示:“我们与 10 大代工客户中的 7 家有积极的合作渠道,并且渠道持续增长,包括 43 家潜在客户和生态系统合作伙伴测试芯片。” 和投资者。“此外,我们继续在 Intel 18A 上取得进展,并且已经与我们的主要客户分享了 PDK 0.5(工艺设计套件)的工程版本,并预计在未来几周内发布最终产品。”

英特尔4nm、3nm、1.8nm时间表更新

在 IEDM 会议上,英特尔分享了其工艺技术路线图以及未来三到四年内可用的芯片设计愿景。正如预期的那样,英特尔的下一代制造工艺——intel 4 和intel 3——有望分别在 2023 年和 2024 年用于大批量制造 (HVM)。此外,该公司的 20A 和 18A 生产节点将在 2024 年为 HVM 做好准备,这意味着 18A 将提前可用。

Intel 4 今天准备就绪,Intel 3 将于 2023 年下半年推出

明年英特尔将发布代号为 Meteor Lake CPU的第 14 代酷睿,这是其首款采用多小(或多块)设计的大众市场客户端处理器,每个小芯片组将使用不同的工艺技术制造。英特尔的 Meteor Lake 产品将包含四个模块:使用intel 4 工艺技术 (又名 7nm EUV)制造的计算模块(CPU 内核)、台积电可能使用其 N3 或 N5 节点生产的图形模块、SoC 模块和 I/O tiles。此外,tiles将使用英特尔的 Foveros 3D 技术相互连接。

Meteor Lake 的计算块可以说是该套件中最令人兴奋的部分,因为它将采用 Intel 4(以前称为 7nm)制造,这是该公司第一个使用极紫外 (EUV) 光刻技术的生产节点。据英特尔称,这种制造工艺已准备好进行大规模生产,不过几个月后它将被部署到 Meteor Lake 计算芯片的 HVM 中。请记住,英特尔于 2021 年 10 月启动了该计算模块,因此该节点现在已准备好投入生产也就不足为奇了。有点出乎意料的是,英特尔并没有证实这种工艺技术是用来制造 Ponte Vecchio 的 Xe-HPC 计算 GPU tile的,就像两年前的那样。

英特尔将在台积电开始使用 EUV 近四年后开始使用 EUV,台积电于 2019 年第二季度开始在其 N7+ 节点上生产芯片。英特尔需要确保其 4nm 级节点性能达到预期并提供良好的良率,因为它将是第一个节点在公司相当不幸的 10nm 系列工艺之后到来,这些工艺在其生命周期的早期没有达到预期的效果,而且成本比公司几年前希望的要高。

由于英特尔必须赶上其竞争对手三星代工厂和台积电,其intel 4 工艺技术将在 2023 ~ 2024 年加入其intel 3 制造节点(3nm 级)。该工艺将在下半年准备好制造2023 年,基于英特尔共享的数据。它将用于制造代号为 Granite Rapids 和 Sierra Forest 的英特尔处理器,这些都是该公司备受瞩目的产品。Sierra Forest 有望成为该公司首款使用节能核心的数据中心 CPU,并将与各种基于 Arm 的高核心数产品竞争。

英特尔已经开始研究 Xeon“Granite Rapids”样品,因此看起来 CPU 的设计已经准备就绪,并且节点本身正在为 HVM 2024 走上正轨。

英特尔首席执行官 Pat Gelsinger 在最近的财报电话会议上表示:“Granite Rapids 的第一步已经走出工厂,良率很好,intel 3 继续按计划取得进展 。” “Emerald Rapids 取得了良好的进展,并有望在 2023 年全年实现,Granite Rapids 在多种配置下运行多个操作系统非常健康,而我们的首款 E-core 产品 Sierra Forest 提供了世界级的每瓦性能,两者都是稳步迈向 2024 年。”

英特尔的 18A 移至 H2 2024

追赶台积电和三星很重要,但要恢复其工艺技术领先地位,英特尔将不得不超越这两个竞争对手。这将在 2024 年的某个时候发生,届时该公司将推出其 20A(20 埃或 2nm)节点,该节点将使用其环栅晶体管品牌 RibbonFET 以及称为 PowerVia 的背面功率传输。英特尔预计其 20A 节点将在 2024 年上半年投产;它将在 2024 年用于为公司代号为 Arrow Lake 的客户端 PC 处理器制造小芯片。

英特尔的 20A 将是业界首个 2nm 级节点,它还将广泛使用 EUV 来最大化晶体管密度,提供不错的性能改进和更低的功耗。到 2024 年,它将与台积电专为提高晶体管密度和性能而设计的第三代 3 纳米级(N3S、N3P)工艺技术展开竞争。这三个节点如何相互叠加还有待观察。尽管如此,英特尔仍为其 20A 工艺设定了很高的标准,因为它同时引入了两项主要创新(GAA、BPD)。

然而,20A 并不是英特尔计划在 2025 年底开始使用的最先进的工艺技术。该公司还在准备其 18A(18 埃,1.8 纳米)生产节点,该节点有望进一步提高 PPA(性能、功率、面积)英特尔及其英特尔代工服务客户的优势。

对于 18A,英特尔最初计划使用具有 0.55 数值孔径 (NA) 光学器件的 EUV 工具,这将提供 8nm 的分辨率(低于当前使用的具有 0.33 NA 的 EUV 工具的 13nm 分辨率)。但 ASML 的 High-NA EUV 设备生产要到 2025 年才能准备就绪,而英特尔的 18A 目标是在 2025 年下半年准备好制造,领先于竞争对手。

由于使用当前一代的 EUV 工具可以通过多重图案化为后 3nm 节点达到 8nm 分辨率(尽管这会延长生产周期并可能影响良率),Intel 愿意在 18A 上承担一些额外的风险并使用ASML的Twinscan NXE:3600D或NXE:3800E在这个节点上制作芯片,因为它相信这将为其带来无可争议的市场领导地位。

事实证明,首批20A和18A测试芯片已经流片。

“在 Intel 20A 和 Intel 18A 上,第一批受益于 RibbonFet 和 PowerVia 的节点,我们的第一批内部测试芯片和主要潜在代工客户的芯片已经流片,并在晶圆厂中运行硅片,”英特尔负责人说。“到 2025 年,我们将继续走上夺回晶体管性能和功率性能领先地位的轨道。”

以上内容转自-半导体行业观察公众号